Pipelining RISC

PIPELINING

Pipeline

adalah cara kerja paralel, dimana komputer mengerjakan 2 atau lebih bagian dari

instruksi secara bersamaan. adapun salah satu teknik yang digunakan untuk

merealisasi Parallel Processing, yaitu dengan membagi operasi ke dalam k-stage

(beberapa tingkatan) atau sub-operasi, sehingga pada satu saat ada k operasi

berjalan yang sekaligus.

Pipelining

merupakan salah satu cara yang paling sering digunakan dalam pararel prosesing.

Sebuah operasi dibagi menjadi sejumlah sub operasi elementer, kita namakan k.

kemudian kita membentuk sebuah sistem dengan banyak stage sebesar k, dan

mengeksekusi sub operasi tersebut pada setiap stage satu demi satu.

pipeling

suatu teknik instruksi yang digunakan dalam desain komputer dan perangkat

elektronik digital lainnya untuk meningkatkan instruksi throughput (jumlah

instruksi yang dapat dijalankan pada waktu yang sama).

Contoh

:

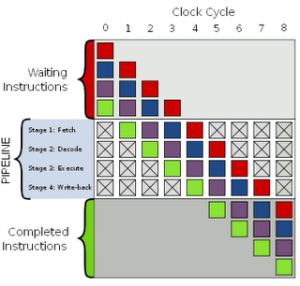

gambar dibawah adalah generik pipa dengan 4 tahapan

gambar dibawah adalah generik pipa dengan 4 tahapan

1.

Fetch

2. Membaca sandi

3. Menjalankan

4. Write-back

2. Membaca sandi

3. Menjalankan

4. Write-back

Abu-abu atas kotak daftar tunggu

instruksi yang akan dilaksanakan; bagian bawah kotak abu-abu adalah daftar

instruksi yang telah selesai, dan tengah kotak putih adalah pipa.

Pelaksanaan

adalah sebagai berikut:

Waktu

Eksekusi

—————————

0 Empat menunggu instruksi yang akan dilaksanakan

1 hijau instruksi yang diambil dari memori

2 hijau adalah instruksi decoded

ungu adalah instruksi yang diambil dari memori

3 hijau instruksi dijalankan (sebenarnya dilakukan operasi) ungu adalah instruksi yang decoded biru instruksi yang diambil

4 hijau instruksi dari hasil ditulis kembali ke daftar file atau memori ungu instruksi yang dijalankan biru adalah instruksi decoded merah instruksi yang diambil

5 hijau instruksi selesai ungu instruksi yang ditulis kembali biru instruksi dijalankan merah adalah instruksi decoded

6 The purple instruksi selesai biru instruksi yang ditulis kembali merah instruksi dijalankan

7 biru instruksi selesai merah instruksi yang ditulis kembali

8 merah instruksi selesai

9 Semua instruksi dijalankan

—————————

0 Empat menunggu instruksi yang akan dilaksanakan

1 hijau instruksi yang diambil dari memori

2 hijau adalah instruksi decoded

ungu adalah instruksi yang diambil dari memori

3 hijau instruksi dijalankan (sebenarnya dilakukan operasi) ungu adalah instruksi yang decoded biru instruksi yang diambil

4 hijau instruksi dari hasil ditulis kembali ke daftar file atau memori ungu instruksi yang dijalankan biru adalah instruksi decoded merah instruksi yang diambil

5 hijau instruksi selesai ungu instruksi yang ditulis kembali biru instruksi dijalankan merah adalah instruksi decoded

6 The purple instruksi selesai biru instruksi yang ditulis kembali merah instruksi dijalankan

7 biru instruksi selesai merah instruksi yang ditulis kembali

8 merah instruksi selesai

9 Semua instruksi dijalankan

—————————————

Kekurangan

pada Pipeline adalah dalam prakteknya, bagaimanapun, prosesor RISC beroperasi

lebih dari satu siklus per instruksi. Prosesor mungkin mengumpulkan hasil dari

data dependensi dan instruksi cabang.

Data

dependensi terjadi bila instruksi tergantung pada hasil dari instruksi

sebelumnya. Instruksi tertentu mungkin perlu data dalam register yang belum

disimpan, sejak itulah pekerjaan yang sebelumnya instruksi yang belum mencapai

tahap yang akan di pipeline.

sebagai

contoh:

add

$r3, $r2, $r1

add $r5, $r4, $r3

add $r5, $r4, $r3

Dalam

contoh ini, instruksi pertama memberitahu prosesor untuk menambahkan isi

register r1 dan r2 dan menyimpan hasilnya dalam register r3. Instruksi kedua

untuk menambahkan r3 dan r4 dan simpan ke r5. Tempat ini kita set instruksi

dalam pipeline. Ketika terjadi instruksi yang kedua itu adalah tahap kedua,

prosesor akan mencoba untuk membaca r3 dan r4 dari register. Ingat, meskipun,

yang pertama adalah instruksi hanya satu langkah di depan kedua, jadi isi r1

dan r2 sedang ditambahkan, tetapi hasilnya belum ditulis ke dalam daftar r3.

Instruksi yang kedua itu tidak dapat dibaca dari register R3 karena belum ditulis

dan belum harus menunggu hingga data yang diperlukan disimpan. Akibatnya, pipa

yang stalled dan sejumlah kosong instruksi dikenal sebagai gelembung pergi ke

dalam pipa. Data dependensi mempengaruhi Pipelines lebih panjang daripada yang

singkat karena memerlukan waktu yang lebih lama untuk instruksi untuk mencapai

akhir pendaftaran tahap-menulis pipa yang panjang.

MIPS solusi untuk masalah ini adalah

kode reordering. Jika, seperti dalam contoh di atas, berikut ini ada petunjuk

tidak ada hubungannya dengan dua pertama, kode dapat diatur ulang sehingga

instruksi yang dijalankan di antara dua tergantung petunjuk dan pipa dapat

mengalir efisien. Tugas kode reordering umumnya mengkompile ke kiri, yang

mengakui data dependensi dan upaya untuk meminimalkan kinerja.

RISC

Pengertian RISC (REDUCET

INSTRUCTION SET COMPUTER)

RISC

(Reduce Instruction Set Computer) atau komputasi set instruksi yang

disederhanakan merupakan sebuah arsitektur komputer atau arsitektur komputasi

modern dengan instruksi-instruksi dan jenis eksekusi yang paling sederhana.

Arsitektur ini digunakan pada komputer dengan kinerja tinggi, seperti komputer

vector. Desain ini juga diimplementasikan pada prosesor komputer lain, seperti

pada beberapa mikroprosesor intel 960, Itanium (IA64) dari Intel Coorporatoin.

Selain itu RISC juga umum dipakai pada Advanced RUSC Machine (ARM) dan Strong

ARM.

Beberapa

elemen penting pada arsitektur RISC :

1.

Set instruksi yang terbatas dan sederhana

2.

Register general-purpose yang berjumlah banyak, atau penggunaan

teknologi kompiler untuk mengoptimalkan pemakaian registernya.

3.

Penekanan pada pengoptimalan pipeline instruksi.

Ditinjau dari jenis set instruksinya,

ada 2 jenis arsitektur komputer, yaitu:

§

Arsitektur komputer dengan kumpulan perintah yang rumit (Complex

Instruction Set Computer = CISC)

§

Arsitektur komputer dengan kumpulan perintah yang sederhana

(Reduced Instruction Set Computer = RISC)

Sumber : https://muhammadfikihramadhani.wordpress.com/2017/12/23/736/

Komentar

Posting Komentar